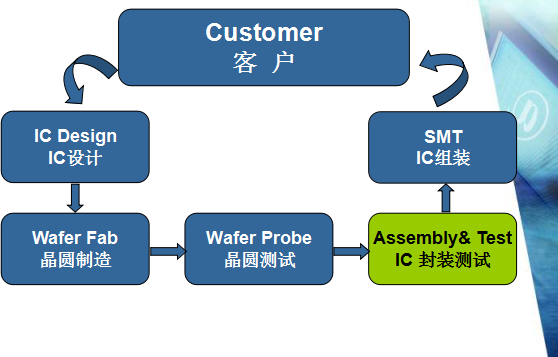

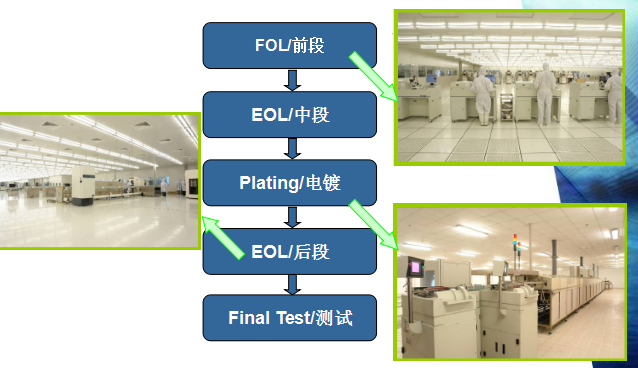

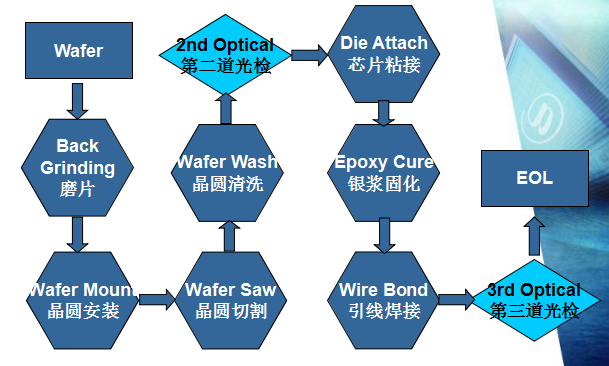

流程

IC Package (IC的封装形式)指芯片(Die)和不同类型的框架(L/F)和塑封料(EMC)形成的不同外形的封装体。

IC Package种类很多,可以按以下标准分类:

按封装材料划分为:

金属封装、陶瓷封装、塑料封装

金属封装主要用于军工或航天技术,无商业化产品;

陶瓷封装优于金属封装,也用于军事产品,占少量商业化市场;

塑料封装用于消费电子,因为其成本低,工艺简单,可靠性高而占有绝大部分的市场份额;

按照和PCB板连接方式分为:

PTH封装和SMT封装

PTH-Pin Through Hole, 通孔式;

SMT-Surface Mount Technology,表面贴装式。

目前市面上大部分IC均采为SMT式的

按照封装外型可分为:

SOT、SOIC、TSSOP、QFN、QFP、BGA、CSP等;

决定封装形式的两个关键因素:

封装效率。芯片面积/封装面积,尽量接近1:1;

引脚数。引脚数越多,越高级,但是工艺难度也相应增加;

其中,CSP由于采用了Flip Chip技术和裸片封装,达到了 芯片面积/封装面积=1:1,为目前最高级的技术;

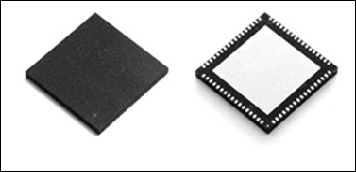

QFN—Quad Flat No-lead Package 四方无引脚扁平封装

SOIC—Small Outline IC 小外形IC封装

TSSOP—Thin Small Shrink Outline Package 薄小外形封装

QFP—Quad Flat Package 四方引脚扁平式封装

BGA—Ball Grid Array Package 球栅阵列式封装

CSP—Chip Scale Package 芯片尺寸级封装

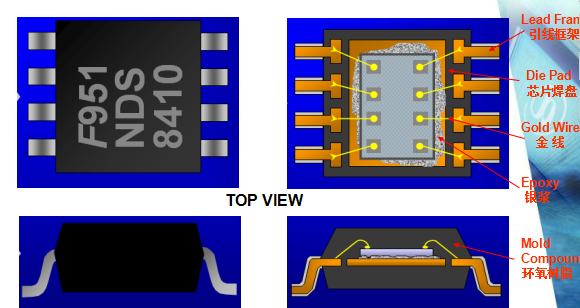

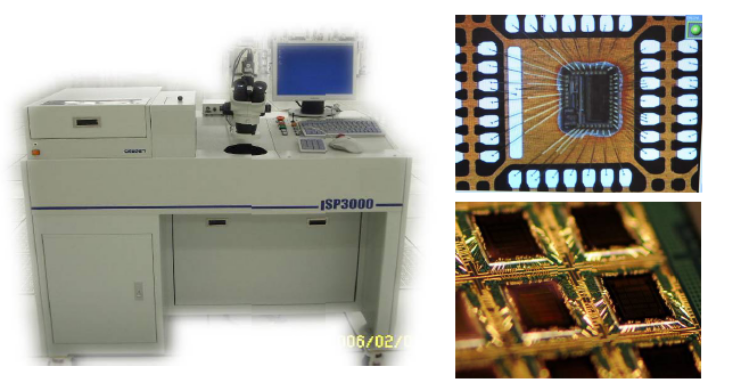

IC Package Structure(IC结构图)

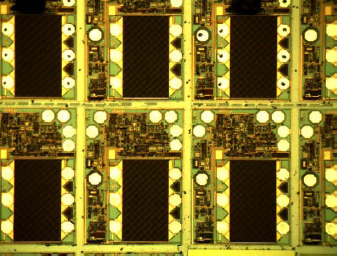

Raw Material in Assembly(封装原材料)【Wafer】晶圆

【Lead Frame】引线框架

提供电路连接和Die的固定作用;

主要材料为铜,会在上面进行镀银、 NiPdAu等材料;

L/F的制程有Etch和Stamp两种;

易氧化,存放于氮气柜中,湿度小 于40%RH;

除了BGA和CSP外,其他Package都会采用Lead Frame, BGA采用的是Substrate;

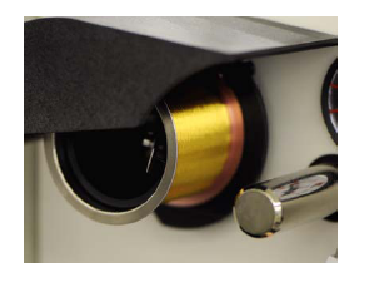

【Gold Wire】焊接金线

实现芯片和外部引线框架的电性和物 理连接;

金线采用的是99.99%的高纯度金;

同时,出于成本考虑,目前有采用铜 线和铝线工艺的。优点是成本降低, 同时工艺难度加大,良率降低;

线径决定可传导的电流;0.8mil, 1.0mil,1.3mils,1.5mils和2.0mils;

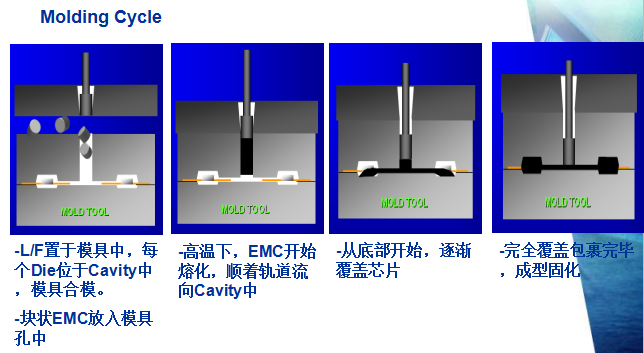

Mold Compound塑封料/环氧树脂主要成分为:环氧树脂及各种添加剂(固化剂,改性剂,脱 模剂,染色剂,阻燃剂等);

主要功能为:在熔融状态下将Die和Lead Frame包裹起来, 提供物理和电气保护,防止外界干扰;

存放条件:零下5°保存,常温下需回温24小时;

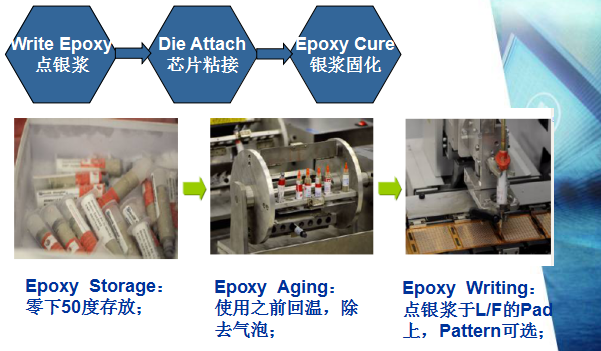

【Epoxy】银浆

成分为环氧树脂填充金属粉末(Ag);有三个作用:将Die固定在Die Pad上; 散热作用,导电作用;

-50°以下存放,使用之前回温24小时;

FOL– Front of Line前段工艺

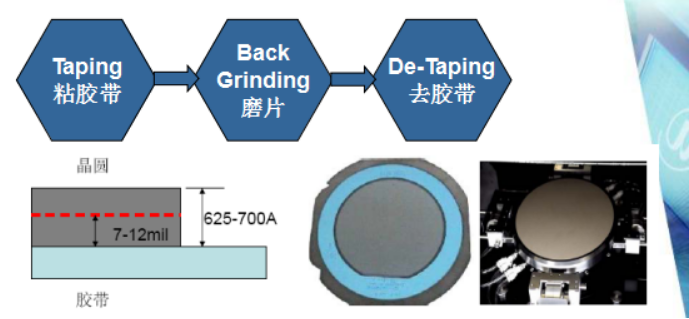

FOL– Back Grinding背面减薄

将从晶圆厂出来的Wafer进行背面研磨,来减薄晶圆达到 封装需要的厚度(8mils~10mils);

磨片时,需要在正面(Active Area)贴胶带保护电路区域 同时研磨背面。研磨之后,去除胶带,测量厚度;

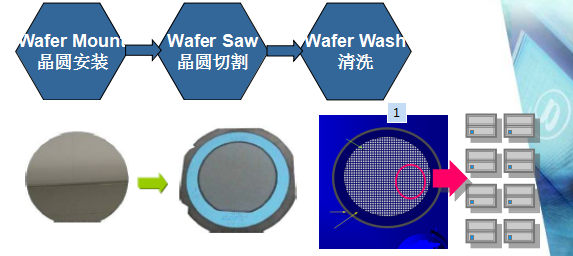

FOL– Wafer Saw晶圆切割

将晶圆粘贴在蓝膜(Mylar)上,使得即使被切割开后,不会散落;

通过Saw Blade将整片Wafer切割成一个个独立的Dice,方便后面的 Die Attach等工序;

Wafer Wash主要清洗Saw时候产生的各种粉尘,清洁Wafer;

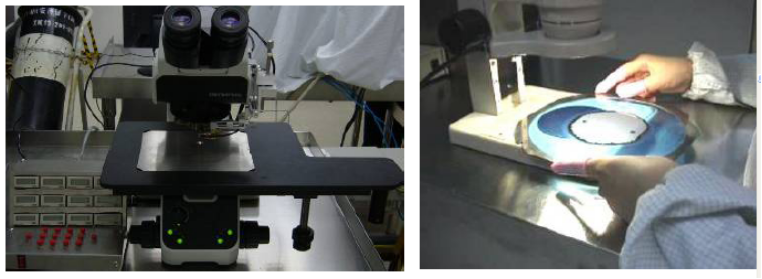

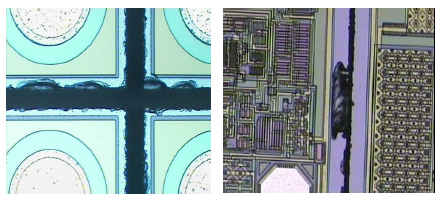

FOL– 2nd Optical Inspection二光检查

主要是针对Wafer Saw之后在显微镜下进行Wafer的外观检查,是否有出现废品。

FOL– Die Attach 芯片粘接

芯片拾取过程:

1、Ejector Pin从wafer下方的Mylar顶起芯片,使之便于 脱离蓝膜;

2、Collect/Pick up head从上方吸起芯片,完成从Wafer 到L/F的运输过程;

3、Collect以一定的力将芯片Bond在点有银浆的L/F 的Pad上,具体位置可控;

4、Bond Head Resolution:X-0.2um;Y-0.5um;Z-1.25um;

5、Bond Head Speed:1.3m/s;

FOL– Epoxy Cure 银浆固化

银浆固化:

175°C,1个小时; N2环境,防止氧化:

Die Attach质量检查:

Die Shear(芯片剪切力)

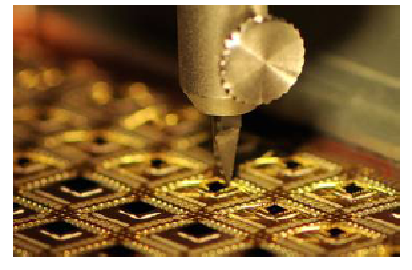

FOL– Wire Bonding 引线焊接

利用高纯度的金线(Au) 、铜线(Cu)或铝线(Al)把 Pad 和 Lead通过焊接的方法连接起来。Pad是芯片上电路的外接 点,Lead是 Lead Frame上的 连接点。

W/B是封装工艺中最为关键的一部工艺。

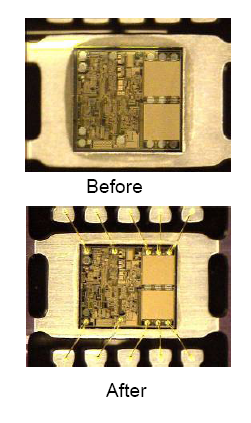

FOL– 3rd Optical Inspection三光检查

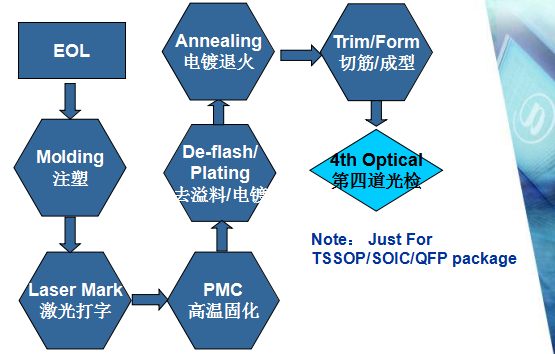

EOL– End of Line后段工艺

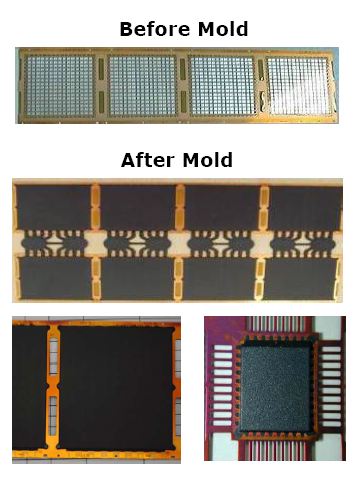

EOL– Molding(注塑)

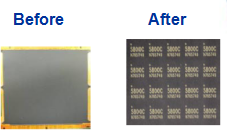

EOL– Laser Mark(激光打字)

在产品(Package)的正面或者背面激光刻字。内容有:产品名称,生产日期,生产批次等;

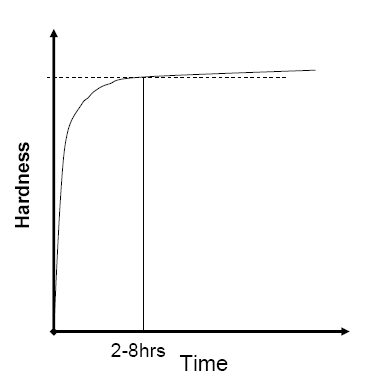

EOL– Post Mold Cure(模后固化)

用于Molding后塑封料的固化,保护IC内部结构,消除内部应力。Cure Temp:175+/-5°C;Cure Time:8Hrs

EOL– De-flash(去溢料)

目的:De-flash的目的在于去除Molding后在管体周围Lead之间 多余的溢料; 方法:弱酸浸泡,高压水冲洗;

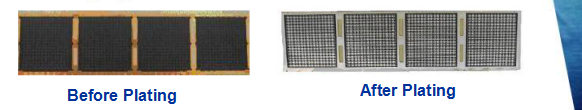

EOL– Plating(电镀)

利用金属和化学的方法,在Leadframe的表面 镀上一层镀层,以防止外界环境的影响(潮湿 和热)。并且使元器件在PCB板上容易焊接及 提高导电性。

电镀一般有两种类型:

Pb-Free:无铅电镀,采用的是>99.95%的高纯 度的锡(Tin),为目前普遍采用的技术,符合 RoHS的要求;

Tin-Lead:铅锡合金。Tin占85%,Lead占 15%,由于不符合RoHS,目前基本被淘汰;

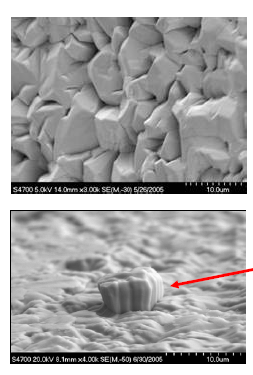

EOL– Post Annealing Bake(电镀退火)

目的:让无铅电镀后的产品在高温下烘烤一段时间,目的在于 消除电镀层潜在的晶须生长(Whisker Growth)的问题; 条件:150+/-5C; 2Hrs;

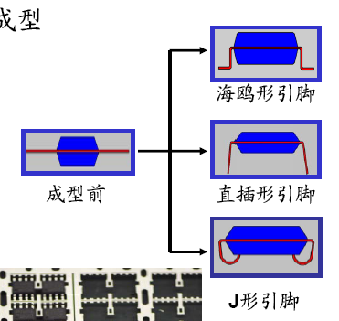

EOL– Trim&Form(切筋成型)

Trim:将一条片的Lead Frame切割成单独的Unit(IC)的过程; Form:对Trim后的IC产品进行引脚成型,达到工艺需要求的形状, 并放置进Tube或者Tray盘中;

EOL– Final Visual Inspection(第四道光检)

在低倍放大镜下,对产品外观进行检查。主要针对EOL工艺可能产生的废品:例如Molding缺陷,电镀缺陷和Trim/Form缺陷等;